DATVexpress Project – a lower cost approach to DATV xmtr

Forum rules

This forum is run by the BATC (British Amateur Television Club), it is service made freely available to all interested parties, please do not abuse this privilege.

Thank you

This forum is run by the BATC (British Amateur Television Club), it is service made freely available to all interested parties, please do not abuse this privilege.

Thank you

DATVexpress Project – a lower cost approach to DATV xmtr

G4GUO and I just finished presenting an introduction to our DATVexpress Project to create a lower-cost transmitter for Digital-ATV…to the 2011 TAPR Digital Communications Conference. The presentation provides an overview and a status on this project being developed by a small team of hams.

The presentation is called:

DATVexpress - a Lower Cost Approach to Digital-ATV Transmitter

The powerpoint file can be found in the DATV Library section on the OCARC web site at:

http://www.W6ZE.org/DATV/

73…de Ken W6HHC

The presentation is called:

DATVexpress - a Lower Cost Approach to Digital-ATV Transmitter

The powerpoint file can be found in the DATV Library section on the OCARC web site at:

http://www.W6ZE.org/DATV/

73…de Ken W6HHC

Last edited by KenW6HHC on Sun Dec 11, 2011 3:57 pm, edited 1 time in total.

Re: DATVexpress Project – a lower cost approach to DATV xmtr

Just a brief note to report on status since the announcement of the DATVexpress project to create a lower-cost DVB-S transmitter board at the TAPR Digital Communications Conference this past September. Progress has been made. The first set of blank PCB boards (first-article) have been fabricated. The first-article prototype board has been assembled and electrically checked-out. The PC is now recognizing the USB2 controller on the board and the first small-step of loading some test code into the FPGA to blink some LEDs has succeeded.

I would like to recognize the team who has contributed so far to Prototype #1:

Electrical design – Art WA8RMC

PCB layout - Tom WB6P

Hand soldering of SMT and power supply checkout - Art WA8RMC

Software and FPGA coding – Charles G4GUO

I have added a new Photo Album for the DATVexpress Project to the yahoo group DigitalDATV...into the PHOTOS area.

http://groups.yahoo.com/group/DigitalATV/

This photo album includes a JPEG of the very first DATVexpress prototype board. As the team announced at TAPR, the complete set of hardware and software design source files will become freely available without restrictions to encourage others to contribute new functions and performance.

Progress to continue…de Ken W6HHC

I would like to recognize the team who has contributed so far to Prototype #1:

Electrical design – Art WA8RMC

PCB layout - Tom WB6P

Hand soldering of SMT and power supply checkout - Art WA8RMC

Software and FPGA coding – Charles G4GUO

I have added a new Photo Album for the DATVexpress Project to the yahoo group DigitalDATV...into the PHOTOS area.

http://groups.yahoo.com/group/DigitalATV/

This photo album includes a JPEG of the very first DATVexpress prototype board. As the team announced at TAPR, the complete set of hardware and software design source files will become freely available without restrictions to encourage others to contribute new functions and performance.

Progress to continue…de Ken W6HHC

Re: DATVexpress Project – a lower cost approach to DATV xmtr

Status report on DATVexpress project - January

Here is another progress update on the DATVexpress Project to design a lower-cost

DVB-S transmitter. (BTW - there is a DATVexpress powerpoint file available in the OCARC DATV Library page at http://www.W6ZE.org/DATV/ .) Since the last update there has been good

news and there has been some disappointing news...

GOOD NEWS

1) The PC can now load the 8051 code onto the USB controller, called FX2.

2) The PC can now download FPGA code through the USB controller.

3) The USB controller can now control the modulator using I2C signaling for

frequency, Symbol-Rate, RF power-level, etc.

4) The FPGA can write to the DACs and onto the QPSK modulator.

5) PROTO#2 board was built to correct an etch-error that affected the modulator

PLL locking. The difficult-to-implement-on-a-populated-board rework for the PLL

is working well.

6) We now have some proper comms between the Linux host and the PCB. EP1 is

being used to download the FPGA code and then for sending I2C commands to the

various chips on the board. EP2 is being used in slave asynchronous mode with

quad buffering to communicate between the USB interface and the FPGA.

SOME DISAPPOINTING NEWS

1) Currently getting some dropouts over the USB2 link. It appears to be a

combination of how our Linux code works, libusb-1.0 and the buffering on the

Express board. Starting to re-write the FPGA code to add some extra buffering on

the board to smooth over the dropouts. There is about 160K of memory on the FPGA

and plan to use about 30% of it for buffering.

2) The RF buffer amplifier chip has tendency to self-oscillate at about 1.9 GHz.

Looks like we did not pay enough attention to nice short etch for the RF

section. We definitely have to revise the etch-traces to resolve this problem.

However the board is still very suitable to continue software programming for

the project.

Progress to continue…de Ken W6HHC

Here is another progress update on the DATVexpress Project to design a lower-cost

DVB-S transmitter. (BTW - there is a DATVexpress powerpoint file available in the OCARC DATV Library page at http://www.W6ZE.org/DATV/ .) Since the last update there has been good

news and there has been some disappointing news...

GOOD NEWS

1) The PC can now load the 8051 code onto the USB controller, called FX2.

2) The PC can now download FPGA code through the USB controller.

3) The USB controller can now control the modulator using I2C signaling for

frequency, Symbol-Rate, RF power-level, etc.

4) The FPGA can write to the DACs and onto the QPSK modulator.

5) PROTO#2 board was built to correct an etch-error that affected the modulator

PLL locking. The difficult-to-implement-on-a-populated-board rework for the PLL

is working well.

6) We now have some proper comms between the Linux host and the PCB. EP1 is

being used to download the FPGA code and then for sending I2C commands to the

various chips on the board. EP2 is being used in slave asynchronous mode with

quad buffering to communicate between the USB interface and the FPGA.

SOME DISAPPOINTING NEWS

1) Currently getting some dropouts over the USB2 link. It appears to be a

combination of how our Linux code works, libusb-1.0 and the buffering on the

Express board. Starting to re-write the FPGA code to add some extra buffering on

the board to smooth over the dropouts. There is about 160K of memory on the FPGA

and plan to use about 30% of it for buffering.

2) The RF buffer amplifier chip has tendency to self-oscillate at about 1.9 GHz.

Looks like we did not pay enough attention to nice short etch for the RF

section. We definitely have to revise the etch-traces to resolve this problem.

However the board is still very suitable to continue software programming for

the project.

Progress to continue…de Ken W6HHC

Re: DATVexpress Project – a lower cost approach to DATV xmtr

Status report on DATVexpress project – May

Some good progress to report:

• Art WA8RMC was able do a work-around on our RF section self-oscillation. Some small coax bypasses etch runs that were too long and too twisty between the modulator and the buffer-RF-amplifier.

• Charles G4GUO was able to sort out the problem we had with dropouts over the USB2 link. USB2 dropouts were due to using the synchronous mode. He switched over to the asynchronous mode for the bulk transfers and can now keep the pipeline full with data (hence no more dropouts).

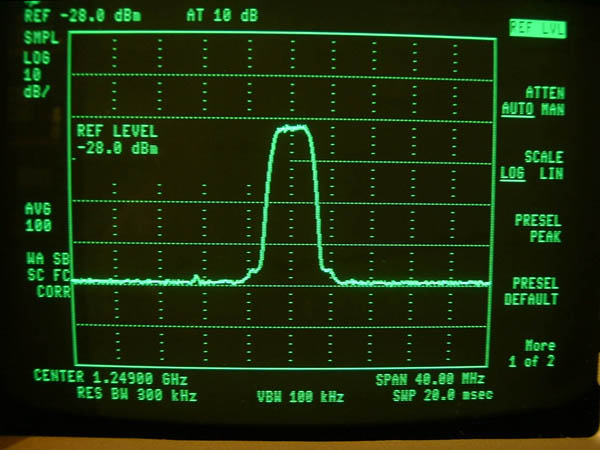

• The big news (in my mind) is that we have transmitted our very first DVB-S video (see the JPEG below). The DATV video was sent using 4 MSymbols/second at FEC = 1/2.

I see this first DVB-S transmission photo as a terrific “proof of concept” step for the DATVexpress project. Charles explains that the software is not the final configuration but is what he calls raw mode and allows the transmission of just about any waveform that can be generated by the P.C. So there is plenty of software work to be done….and an etch-clean-up effort to be done.

Two areas that we need to focus on next are: adding code for an interpolating filter inside the FPGA so the sample can be at a higher rate to reduce aliasing (currently just 5M samples/sec) and to solve a hardware issue with IQ imbalance (not a show stopper).

Any questions are welcome…de Ken W6HHC

Some good progress to report:

• Art WA8RMC was able do a work-around on our RF section self-oscillation. Some small coax bypasses etch runs that were too long and too twisty between the modulator and the buffer-RF-amplifier.

• Charles G4GUO was able to sort out the problem we had with dropouts over the USB2 link. USB2 dropouts were due to using the synchronous mode. He switched over to the asynchronous mode for the bulk transfers and can now keep the pipeline full with data (hence no more dropouts).

• The big news (in my mind) is that we have transmitted our very first DVB-S video (see the JPEG below). The DATV video was sent using 4 MSymbols/second at FEC = 1/2.

I see this first DVB-S transmission photo as a terrific “proof of concept” step for the DATVexpress project. Charles explains that the software is not the final configuration but is what he calls raw mode and allows the transmission of just about any waveform that can be generated by the P.C. So there is plenty of software work to be done….and an etch-clean-up effort to be done.

Two areas that we need to focus on next are: adding code for an interpolating filter inside the FPGA so the sample can be at a higher rate to reduce aliasing (currently just 5M samples/sec) and to solve a hardware issue with IQ imbalance (not a show stopper).

Any questions are welcome…de Ken W6HHC

Re: DATVexpress Project – a lower cost approach to DATV xmtr

This is really a good news!

There are currently 2 open source, FPGA based, DVB-S modulators under development : Digilite-ZL and DATV-Express.

I think the DATV-Express is more "modern" because it uses very integrated components : DAC, and PLL-Modulator. The desigh should be more compact, and can adapt to a large variety of symbol rates with the same hardware (no need to have different hardware Nyquist filters).

I am very interested about such projetcs. Thank you for all your good job! It seems like a "professionnal" project.

I have some questions :

* I understand that the FEC encoding is done on the PC side (like Digilite UK). Do you plan to transfer it to the FPGA side?

* Do you plan the FEC to be tuned? Like in Digilite software? Other FEC ratios than just 1/2 (which is the easiest to compute)?

* Do you plan to add a TS input (SPI or equivalent)? This would be helpfull to use the DATV-Express board without a PC, in a repeater for example. This interface could be compatible with SR-System boards for example. But without FEC encoding on FPGA, it would be impossible.

Leon.

There are currently 2 open source, FPGA based, DVB-S modulators under development : Digilite-ZL and DATV-Express.

I think the DATV-Express is more "modern" because it uses very integrated components : DAC, and PLL-Modulator. The desigh should be more compact, and can adapt to a large variety of symbol rates with the same hardware (no need to have different hardware Nyquist filters).

I am very interested about such projetcs. Thank you for all your good job! It seems like a "professionnal" project.

I have some questions :

* I understand that the FEC encoding is done on the PC side (like Digilite UK). Do you plan to transfer it to the FPGA side?

* Do you plan the FEC to be tuned? Like in Digilite software? Other FEC ratios than just 1/2 (which is the easiest to compute)?

* Do you plan to add a TS input (SPI or equivalent)? This would be helpfull to use the DATV-Express board without a PC, in a repeater for example. This interface could be compatible with SR-System boards for example. But without FEC encoding on FPGA, it would be impossible.

Leon.

Re: DATVexpress Project – a lower cost approach to DATV xmtr

Hi Leon,

Your wrote <“I have some questions : >

* I understand that the FEC encoding is done on the PC side (like Digilite UK). Do you plan to transfer it to the FPGA side?

I have inserted the “system block diagram” for a DATVexpress transmitter. The left-hand “yellow block” lists the main functions performed inside the PC. The right-hand “yellow block" lists the main functions that will be performed inside the DATVexpress board.

The DATVexpress block diagram shows that current project plans are to keep the FEC processing inside the PC.

* Do you plan the FEC to be tuned? Like in Digilite software? Other FEC ratios than just 1/2 (which is the easiest to compute)?

Yes, the FEC setting can be configured inside the PC (using the GUI) to the desired value.

* Do you plan to add a TS input (SPI or equivalent)? This would be helpfull to use the DATV-Express board without a PC, in a repeater for example. This interface could be compatible with SR-System boards for example. But without FEC encoding on FPGA, it would be impossible.

I understand your point about the location of the FEC processing. Many things are possible…but for now, the first plan by the team is to only complete the system software and the PCBA and the board coding as seen in the system diagram. As the team announced at TAPR conference in 2011, the complete set of hardware and software design source files will become freely available without restrictions to encourage others to contribute new functions and performance.

Just as a reminder to interested readers, a link to the entire PowerPoint file presented at TAPR is provided in the first entry of this forum-topic-thread.

73…de Ken W6HHC

Your wrote <“I have some questions : >

* I understand that the FEC encoding is done on the PC side (like Digilite UK). Do you plan to transfer it to the FPGA side?

I have inserted the “system block diagram” for a DATVexpress transmitter. The left-hand “yellow block” lists the main functions performed inside the PC. The right-hand “yellow block" lists the main functions that will be performed inside the DATVexpress board.

The DATVexpress block diagram shows that current project plans are to keep the FEC processing inside the PC.

* Do you plan the FEC to be tuned? Like in Digilite software? Other FEC ratios than just 1/2 (which is the easiest to compute)?

Yes, the FEC setting can be configured inside the PC (using the GUI) to the desired value.

* Do you plan to add a TS input (SPI or equivalent)? This would be helpfull to use the DATV-Express board without a PC, in a repeater for example. This interface could be compatible with SR-System boards for example. But without FEC encoding on FPGA, it would be impossible.

I understand your point about the location of the FEC processing. Many things are possible…but for now, the first plan by the team is to only complete the system software and the PCBA and the board coding as seen in the system diagram. As the team announced at TAPR conference in 2011, the complete set of hardware and software design source files will become freely available without restrictions to encourage others to contribute new functions and performance.

Just as a reminder to interested readers, a link to the entire PowerPoint file presented at TAPR is provided in the first entry of this forum-topic-thread.

73…de Ken W6HHC

Re: DATVexpress Project – a lower cost approach to DATV xmtr

We are using less that 5% of the resources on the FPGA so if someone

wanted to move the FEC onto to the board for DVB-S they could.

For things like DVB-S2 and DVB-T2 because they use LDPC

(low density parity check) codes which have very long blocks

there would not be enough RAM.

We live by the ethos that "if you build it they will come" i.e if we provide

the hardware others will want to hack the software . It only takes one

. It only takes one

person to write the code and then share it.

The host software currently supports all the DVB-S FEC rates and also does

DVB-T both 2K and 8K modes. I am part way though implementing DVB-S2.

- Charles G4GUO

wanted to move the FEC onto to the board for DVB-S they could.

For things like DVB-S2 and DVB-T2 because they use LDPC

(low density parity check) codes which have very long blocks

there would not be enough RAM.

We live by the ethos that "if you build it they will come" i.e if we provide

the hardware others will want to hack the software

person to write the code and then share it.

The host software currently supports all the DVB-S FEC rates and also does

DVB-T both 2K and 8K modes. I am part way though implementing DVB-S2.

- Charles G4GUO

Re: DATVexpress Project – a lower cost approach to DATV xmtr

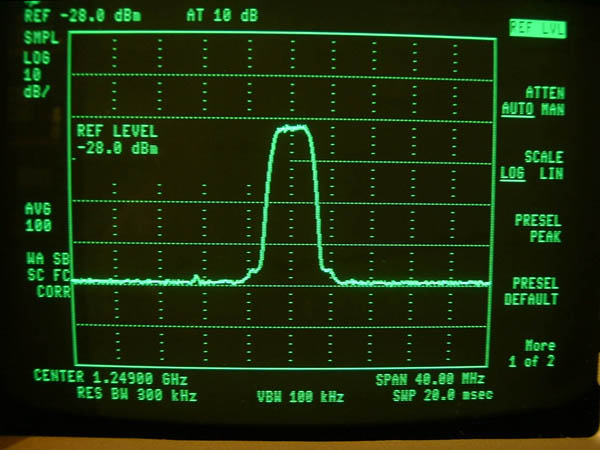

In case anyone is interested and doesn't read my blog I have

posted a picture taken from my spectrum analyser showing

the output of the DATV Express card. It uses a 49 tap filter,

root raised cosine response with x/sin(x) compensation, 16 bit

filter coefficients and a 14 bit DAC on the output.

Sampling is at 20 MHz and the Analogue Nyquist filter is at 5MHz.

The Analyser is set to a 40 MHz sweep.

- Charles G4GUO

posted a picture taken from my spectrum analyser showing

the output of the DATV Express card. It uses a 49 tap filter,

root raised cosine response with x/sin(x) compensation, 16 bit

filter coefficients and a 14 bit DAC on the output.

Sampling is at 20 MHz and the Analogue Nyquist filter is at 5MHz.

The Analyser is set to a 40 MHz sweep.

- Charles G4GUO